Correct option is C

Given:

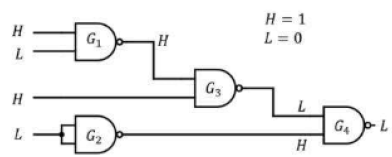

- A digital circuit with logic levels H (High = 1) and L (Low = 0).

- The circuit contains NAND gates G1, G2, G3, and G4.

- Identify which gate is not behaving as an ideal NAND gate based on the observed logic levels.

Solution:

Behavior of an Ideal NAND Gate:

- A NAND gate outputs Low (L) only when both inputs are High (H).

- For all other combinations of inputs, the output is High (H).

Analyze Each Gate:

- Gate G1: Check the input and output logic levels. If the output matches the expected behavior of a NAND gate, G1 is ideal.

- Gate G2: Similarly, compare the input and output levels. Ensure that it follows the truth table of a NAND gate.

- Gate G3: Verify the input and output logic levels to confirm if it behaves as an ideal NAND gate.

- Gate G4: Analyze its input and output levels. If there is a mismatch between the observed output and the expected behavior, G4 is not functioning as an ideal NAND gate.

Conclusion:

Based on the analysis of the circuit, the behavior of G4 does not align with the truth table of an ideal NAND gate.

The correct answer is: (c) G4.